亿佰特小编前文详细的了各种工业以太网技术浅析 、以太网有什么缺陷?工业以太网又有何优势?、以太网与rs232和rs485接口数据无线传输详解和什么是工业以太网?工业以太网有哪些类型?等等以太网相关常见支持介绍,小忆就以太网数据链层—PHY、MAC和 MII基础知识做详细介绍。详细内容请看下文:

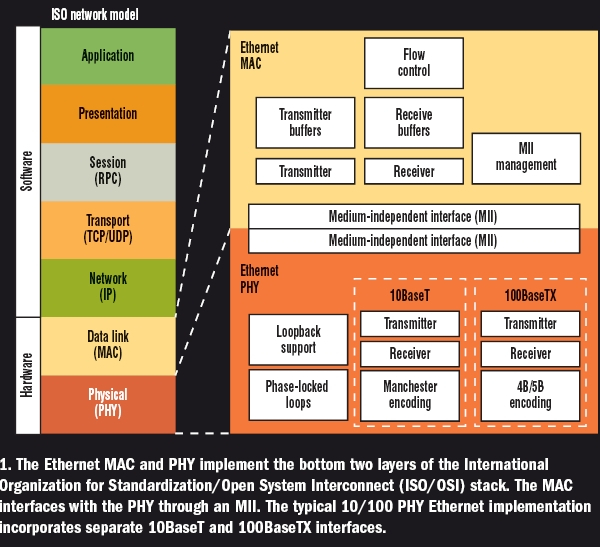

PHY是物理接口收发器,它实现物理层。包括 MII/GMII (介质独立接口) 子层、PCS (物理编码子层) 、PMA (物理介质附加) 子层、PMD (物理介质相关) 子层、MDI 子层。定义了数据传送与接收所需要的电与光信号、线路状态、时钟基准、数据编码和电路等,并向数据链路层设备提供标准接口。物理层的芯片称之为PHY。

MAC是 Media Access Control 的缩写,即媒体访问控制子层协议。该协议位于 OSI 七层协议中数据链路层的下半部分,主要负责控制与连接物理层的物理介质。在发送数据的时候,MAC 协议可以事先判断是否可以发送数据,如果可以发送将给数据加上一些控制信息,最终将数据以及控制信息以规定的格式发送到物理层;在接收数据的时候,MAC协议首先判断输入的信息是否发生传输错误,如果没有错误,则去掉控制信息发送至 LLC 层。以太网 MAC 由IEEE 802.3以太网标准定义。

MII即媒体独立接口,也叫介质无关接口。它是IEEE-802.3定义的以太网行业标准。它包括一个数据接口,以及一个MAC和PHY之间的管理接口。数据接口包括分别用于发送器和接收器的两条独立信道。每条信道都有自己的数据、时钟和控制信号。

MII数据接口总共需16个信号。管理接口是个双信号接口:一个是时钟信号,另一个是数据信号。通过管理接口,上层能监视和控制PHY。

由此可见,MAC 和 PHY,一个是数据链路层,一个是物理层;两者通过 MII 传送数据。

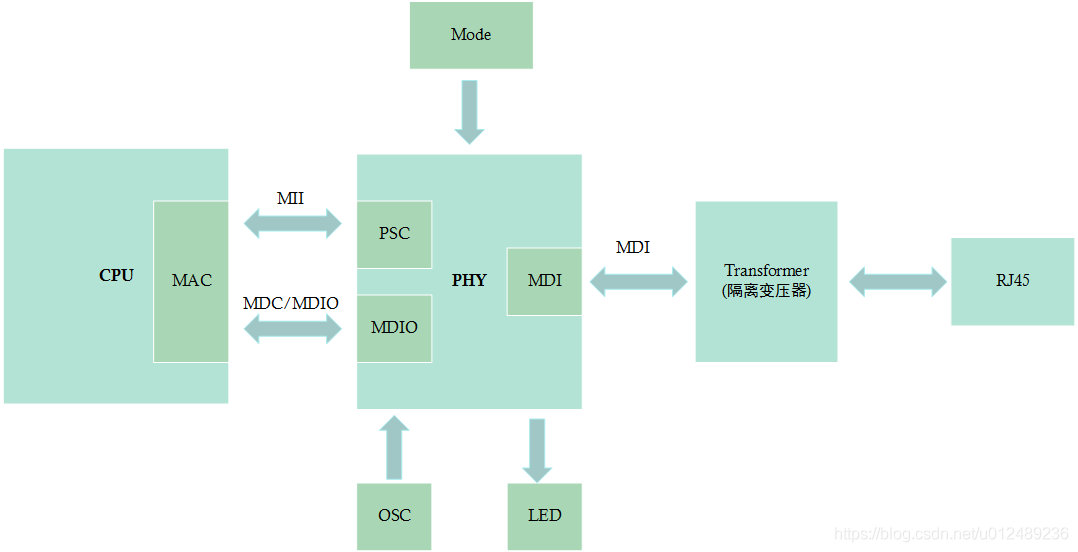

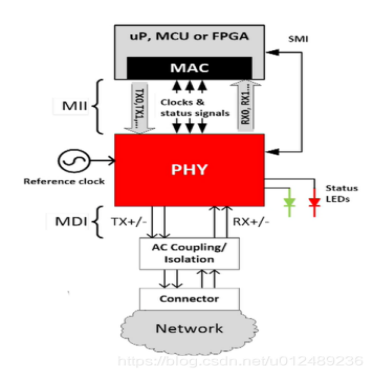

从硬件的角度来分析,以太网的电路接口一般由CPU、MAC(Media Access Control)控制器和物理层接口(physical Layer PHY)组成:

对于上述三部分,并不一定都是独立的芯片,主要有以下几种情况:

·CPU内部集成了MAC和PHY,难度较高;

·CPU内部集成MAC,PHY采用独立芯片(主流方案);

·CPU不集成MAC和PHY,MAC和PHY采用独立芯片或者集成芯片(高端采用)

PHY整合了大量模拟硬件,而MAC是典型的全数字器件,芯片面积及模拟/数字混合架构的原因,是将MAC集成进微控制器而将PHY留在片外的原因。更灵活、密度更高的芯片技术已经可以实现MAC和PHY的单芯片整合;

·以常用的CPU内部集成MAC,PHY采用独立的芯片方案,虚线内表示CPU和MAC集成在一起,PHY芯片通过MII接口与CPU上的MAC互联;

对于这种方案,其硬件方案比独立的更简单,PHY与MAC之间有以下两个重要的硬件接口:

·MDIO总线接口,主要是完成CPU对于PHY芯片的寄存器配置;

·MII即媒体独立接口,也叫介质无关接口。常见的有MII、RMII、GMII、RGMII等。“媒体独立”表明在不对 MAC 硬件重新设计或替换的情况下,任何类型的 PHY 设备都可以正常工作。MII 数据接口总共需要16个信号,包括:

·transmit data - TXD[3:0]

·transmit strobe - TX_EN

·transmit clock - TX_CLK

·transmit error - TX_ER/TXD4

·receive data - RXD[3:0]

·receive strobe - RX_DV

·receive clock - RX_CLK

·receive error - RX_ER/RXD4

·collision indication - COL

·carrier sense - CRS

一般说来,包括:IC 对 PHY 作读取与写入用的一组信号:MDC(clock),MDIO(data) 作为 data sampling reference 用的两组 clock。频率应为 25MHz(TX_CLK,RX_CLK)各4-bit 的输出、输入 Bus(TX[0:3],RX[0:3])。通知对方准备输入数据的输出、输入的启动信号(TX_EN)。输出、输入的错误通知信号(TX_ER,RX_ER)。得到有效输入数据的通知信号(RX_DV)。网络出现拥塞的 colision 信号(Col)。

做为carrier 回复用的信号(CRS),电位可使用+5V 或+3.3V。

MII 以 4bit,即半字节方式双向传送数据,时钟速率 25MHz,其工作速率可达 100Mb/s。MII传递了网络的所有数据和数据的控制,而 MAC对PHY 的工作状态的确定和对 PHY 的控制则是使用 SMI ( Serial Management Interface) 界面通过读写PHY的寄存器来完成的。PHY 里面的部分寄存器是 IEEE 定义的,这样 PHY 把自己的目前的状态反映到寄存器里面,MAC 通过 SMI 总线不断地读取 PHY 的状态寄存器以得知目前 PHY 的状态,例如连接速度,双工能力等。当然也可以通过 SMI 设置 PHY 的寄存器达到控制的目的,例如流控地打开关闭,自协商模式还是强制模式等。

不论是物理连接的MII 总线和 SMI 总线还是 PHY 的状态寄存器和控制寄存器都是有IEEE 802.3标准协议的规范的,因此不同公司的 MAC 和 PHY 一样可以协调工作。当然为了配合不同公司的 PHY 的自己特有的一些功能,驱动需要做相应的修改。

SMI是MAC内核访问PHY寄存器接口,它由两根线组成、双工,MDC为时钟,MDIO为双向数据通信,原理上跟I2C总线很类似,也可以通过总线访问多个不同的PHY。

·两线制:MDC(时钟线)和MDIO(数据线)。

·时钟频率:2.5MHz

·通信方式:总线制,可同时接入的PHY数量为32个

·通过SMI接口,MAC芯片主动地轮询PHY层芯片,获得状态信息,并发出命令信息。

后来为了支持千兆网口,也就开始有了千兆网的MII接口,也就是GMII接口。现在比较常用的是RGMII,减小了MAC和PHY之间的引脚数量。数据信号和控制信号混合在一起,并且在工作时钟的上升沿和下降沿同时采样,其对应关系如下:

10M带宽对应的是2.5MHz,因为4bit*2.5M=10Mbps

100M带宽对应的是25MHz,因为4bit*25M=100Mbps

1000M带宽对应的是125MHz,4bit*125M=1000Mbps,因为250MHz频率太高,所以采用双边沿采样技术(会带来设计复杂度)。

今天的分享就到这里啦,EBYTE每一天都致力于更好的助力物联化、智能化、自动化的发展,提升资源利用率,更多串口服务器产品和以太网模组配置应用案例,感兴趣的小伙伴可以登录我们的亿佰特官网和企业公众号(微信号:cdebyte)进行了解,也可以直接拨打400电话咨询技术专员!

相关文章推荐:

7 X 24 销售服务热线

4000-330-990©© 成都亿佰特电子科技有限公司【版权所有】 蜀ICP备13019384号