SPI总线的英文全称为Serial Peripheral Interface,顾名思义为串行外设接口。SPI通信协议是一种同步串行通信接口规范,主要应用于嵌入式系统中的短距离通信。该接口由摩托罗拉在20世纪80年代中期开发,后发展成了行业规范。

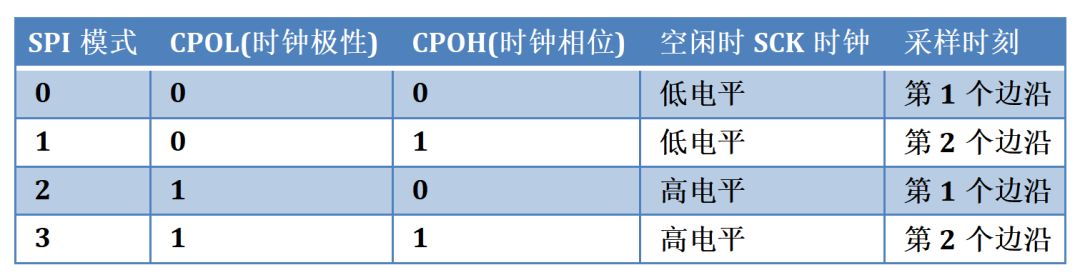

SPI通信中有4种不同的操作模式,不同的从机设备可能在出厂时就被设置好了某种模式,并且无法更改。但是SPI通信必须处于同一种模式下才能进行。因此我们应该对自己手里的SPI主机设备进行模式的配置,也就是通过CPOL(时钟极性)和CPHA(时钟相位)来控制SPI主设备的通信模式,具体如下:

时钟极性(CPOL)定义了SCLK时钟线空闲状态时的电平:

1.CPOL=0,即SCLK=0,表示SCLK时钟信号线在空闲状态时的电平为低电平,因此有效状态为高电平。

2.CPOL=1,即SCLK=1,表示SCLK时钟信号线在空闲状态时的电平为高电平,因此有效状态为低电平。

时钟相位(CPHA)定义了数据位相对于时钟线的时序(即相位):

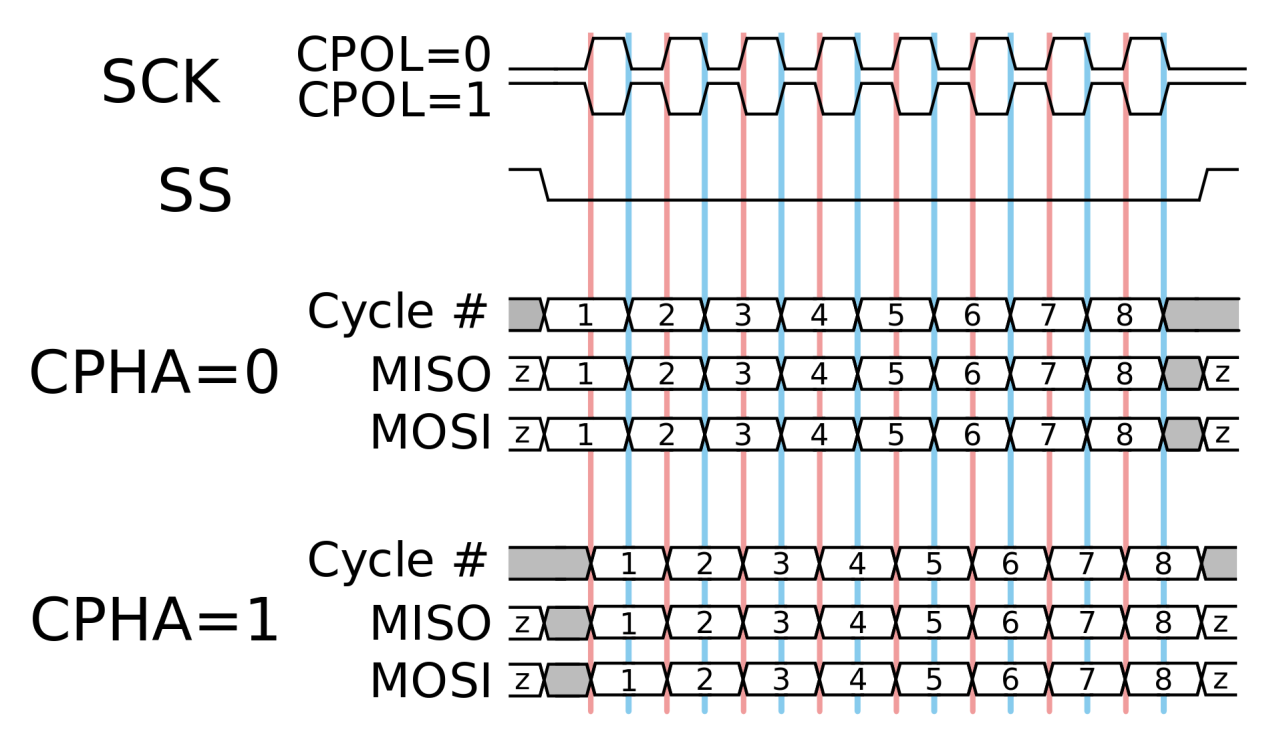

1.CPHA=0,即表示输出(out)端在上一个时钟周期的后沿改变数据,而输入(in)端在时钟周期的前沿(或不久之后)捕获数据。输出端保持数据有效直到当前时钟周期的尾部边缘。对于第一个时钟周期来说,第一位的数据必须在时钟前沿之前出现在MOSI线上。也就是一个CPHA=0的周期包括半个时钟空闲和半个时钟置位的周期。

2.CPHA=1,即表示输出(out)端在当前时钟周期的前沿改变数据,而输入(in)端在时钟周期的后沿(或不久之后)捕获数据。输出端保持数据有效直到下一个时钟周期的前沿。对于最后一个时钟周期来说,从机设备在片选信号消失之前保持MISO信号线有效。也就是一个CHPA=1的周期包括半个时钟置位和半个时钟空闲的周期。

Note:此处的前沿和后沿的意思表示在每个周期中第一个出现的边沿和最后一个出现的边沿。总的来说则为:当时钟为正向时钟时,时钟线的上升沿为前沿,时钟的下降沿为后沿,反之。

如下表,为SPI通信的4种模式:

下图显示了时钟极性和相位的时序图。红线表示时钟的前沿,蓝线表示时钟的后沿。

SPI通信协议的优点在于它有着比I2C更高的吞吐量,不被最大时钟速度所限制,可实现潜在的高速、极为简单的硬件接口,外围电路使用的上拉电阻是比I2C协议更少的,这意味着它比I2C的功耗更低、从机的时钟来源来自主机设备,无需新增精密振荡器、从机不需要唯一的地址、相对于并行接口而言,使用的引脚数目大大减少等优点。但SPI通信协议同时有着一定的缺点,例如SPI没有带内寻址、当使用多个不同模式的从机设备时,主机设备切换模式时重新初始化,会使得访问从机设备速度变慢、SPI从机设备没有硬件流控,只能通过主机自主地延迟下个时钟周期到来的时间、仅能在短距离通信等缺点。但能在避免SPI的缺点的方向来应用SPI的话,SPI总线接口的优点让它远远优于其他通信协议。

今天的分享就到这里啦,EBYTE每一天都致力于更好的助力物联化、智能化、自动化的发展,提升资源利用率,更多串口服务器、数传电台、lora模块等无线数传模块产品更多资料,感兴趣的小伙伴可以登录我们的亿佰特官网进行了解,也可以直接拨打400电话咨询技术专员!

相关阅读:

7 X 24 销售服务热线

4000-330-990©© 成都亿佰特电子科技有限公司【版权所有】 蜀ICP备13019384号