TTL门电路是一种集成电路,通过使用双极性晶体管组合来做到具有驱动能力的逻辑输出。TTL电路最重要的特性是门的输入在未连接时将为逻辑高电平。

在硬件电路中,会用到逻辑门这样的数字器件,对于这样的数字器件,从内部工艺结构来份的话主要有两个大的分支:一个是晶体管构成的,另一个是场效应管构成的。而晶体管构成的门电路,被称为TTL门电路。

TTL门电路也分很多种,比如说非门、与非门、或非门、与或非门以及OC输出的与非门。虽然种类多,但是基本的工作原理都是类似的。以常用的与非门电路为例对其工作原理进行介绍。

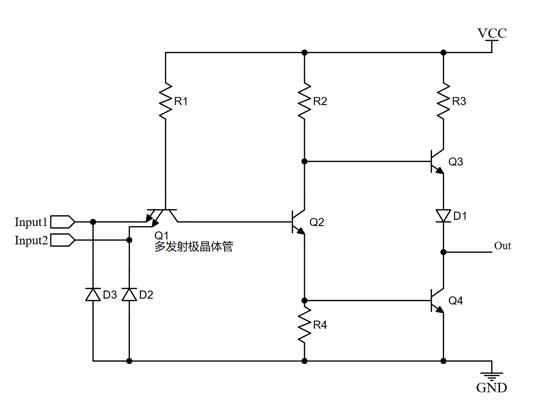

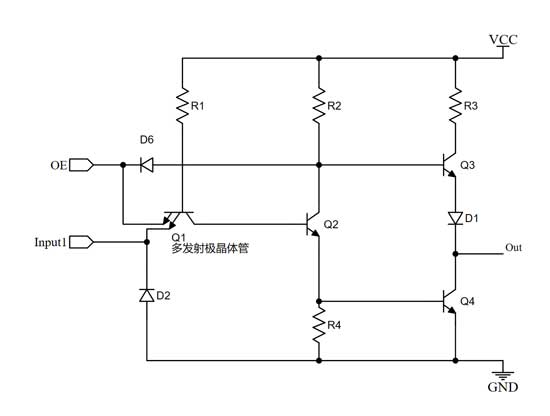

图1 非门的TTL电路

从图1中可以看出非门电路是由Q1输入级、Q2中间级以及Q3、Q4输出级组成。

1、输入级:Q1从结构上把它看成由二极管构成的,两个二极管的P结背靠背,N结分别连接输入和Q2的基极。

2、中间级:由三极管Q2和电阻R2、R4组成。在电路的开通过程中利用Q2的放大作用,为输出管Q3和Q4提供较大的基极电流,加速了输出管的导通。所以,中间级的作用是提高输出管的开通速度,改善电路的性能。

3、输出级:由三极管Q3、Q4、二极管D1和电阻R3组成。从图中可以看出,输出级由三极管Q4实现逻辑非的运算。但在输出级电路中用三极管Q3、二极管D1和R3组成的有源负载来使输出级具有较强的负载能力。其中D1可以起到三极管be反向击穿的保护作用。

1、当输入端Input为逻辑低电平时,电流流经R1至Input,Q1晶体管导通,此时Vb(Q2)的电压小于Vbe导通电压0.7V,Q2晶体管截止。此时由于R2与R4的存在,使Q3导通、Q4截止,在Out上输出高电平。由图1中输出结构可知,此时输出高电平电压将为:Vout = Vcc - Vce -Vd1 ≈ Vcc-1V。

2、当输入端Input为逻辑高电平时,Q1晶体管截止,此时电流流经R1和Q1的PN结,流向Q2的基极,Q2晶体管导通。此时Q4导通,Q3的基极电压约为1V,而Q3的导通电压需要Vb3约为1.7V,Q3将不导通,则在Out上输出低电平。由图1中输出结构可知,此时输出低电平电压将为:Vout ≤ 0.4V。

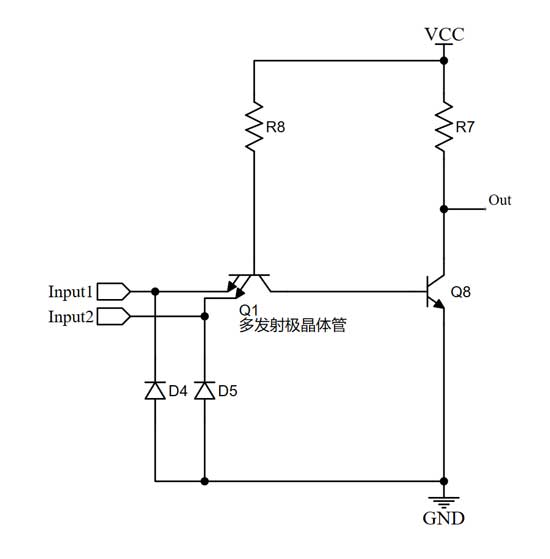

TTL的多路与输入可以由图1简化而来,由于作为逻辑输入通常不需要很大的功率,可以去掉功率部分,只保留逻辑部分,如图二所示。

图2 2路TTL输入

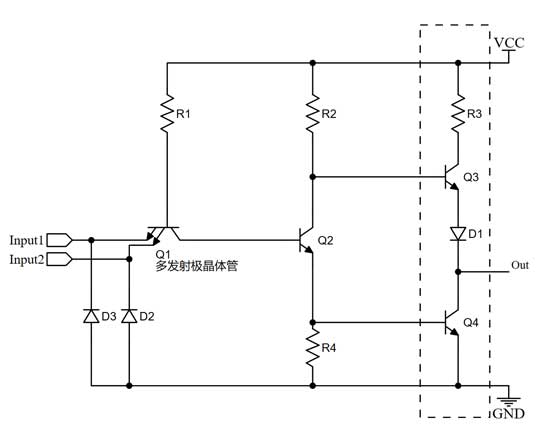

在下图所示的电路中,阴影部分表示图腾柱输出。三极管Q 3、Q 4、二极管D1和限流电阻R 3构成TTL的图腾柱输出结构,可以为外部设备提供较强的供电能力。

图3 图腾柱输出电路

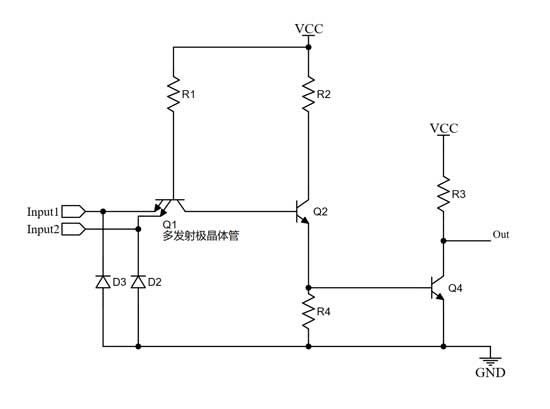

TTL逻辑的开漏输出电路如下图所示。在此配置中,取消了晶体管 Q 3、D1和上拉电阻。取而代之的是外部上拉电阻R3以确保正常运行,如图所示。

图4 开漏型TTL输出

三态门输出电路结构如下图所示,其输出具有三种输出状态:高、低和高阻。

当OE使能为低电平时,Q3、Q4都处于关闭状态,此时的输出端呈现高阻态,输出状态浮空。当OE使能为高电平时,输出的状态由输入决定。

图5 三态门输出电路

今天的分享就到这里啦,EBYTE每一天都致力于更好的助力物联化、智能化、自动化的发展,提升资源利用率,更多产品更多资料,感兴趣的小伙伴可以登录我们的亿佰特官网和企业公众号(微信号:cdebyte)进行了解,也可以直接拨打400电话咨询技术专员!

7 X 24 销售服务热线

4000-330-990©© 成都亿佰特电子科技有限公司【版权所有】 蜀ICP备13019384号