这篇文章并不是介绍怎编写Makefile, 是理解 “基于目标分层” 的方式理解来理解一个工具,定义一个设计或者部署一套代码的。

说明一下,Makefile最初是用来解决C语言的编译问题的,所以和C的关系特别密切,但并不是说Makefile只能用来解决C的编译问题。你用来处理Java一点问题没有,但对于Java,显然ant比Makefile处理得更好。但是那是细节,你理解了Makefile,理解ant就没有什么难度了。Makefile本身的格式也不是什么标准,不同的make工具对Makefile本身怎么写细节是不一样的。本文介绍的是这个工具的思想原理,细节你要自己看对应的手册。

Makefile解决的是编译的问题。编译有什么问题呢?比如说,你有3个C文件。foo.c, bar.c, main.c三个C文件,你要编译成一个app.exe,则会有这样的命令:

gcc -Wall -c foo.c -o foo.o

gcc -Wall -c bar.c -o bar.o

gcc -Wall -c main.c -o main.o

gcc main.o foo.o bar.o -lpthread -o app.exe

按Unix程序员的惯例,凡是要一次次重新执行的命令,都应该写成脚本,变成“一个动作”。所以,你会把上面这个命令序列写成一个build.sh,每次编译你只要执行这个脚本问题就解决了。

但是,这个脚本依然有问题,假设我修改了foo.c,但我没有修改bar.c和main.c,那么执行这个脚本是很浪费的,因为它会无条件也重新编译bar.c和main.c。

所以,这个脚本更合理的写法应该是这样的:

[ foo.o -ot foo.c ] && gcc -Wall -c foo.c -o foo.o

[ bar.o -ot bar.c ] && gcc -Wall -c bar.c -o bar.o

[ main.o -ot main.o] && gcc -Wall -c main.c -o main.o

[ app.executable -ot main.o ] && [ app.executable -ot foo.o ] && [ app.executable -ot bar.o ] && gcc main.o foo.o bar.o -lpthread -o app.executable

这很复杂是不是?同样按Unix程序员的一般作风,如果你面对一个问题,不要尝试重新去定义这个问题,而是看它和原来的问题相比,多出来的问题是什么,尝试解决那个多出来的问题就好了。那么这里,多出来的问题就是文件修改时间比较。这个就是Makefile要解决的基本问题了。我们定义一种新的“脚本语言”(只是不用sh/bash/tch来解释,而是用make来解释),可以用很简单的方法来说明我们需要做的文件比较。这样上面的脚本就可以写成这个样子了:

foo.o: foo.c

gcc -Wall -c foo.c -o foo.o

bar.o: bar.c

gcc -Wall -c bar.c -o woo.o

main.o: main.c

gcc -Wall -c main.c -o main.o

app.executable: foo.o bar.o main.o

这就是Makefile解决的原始问题。Makefile不是必须的,但它能减少你很多麻烦。

Make工具需要一个称为makefile的文件来告诉Make如何工作。一般来说,makefile告诉Make如何去编译并且链接一个程序。

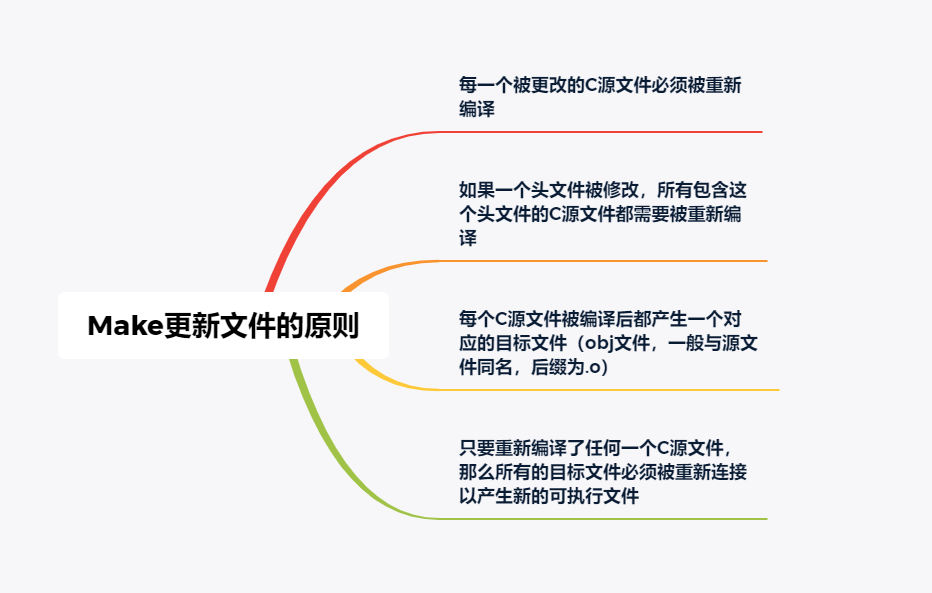

了解以上四个原则是很有必要的,当我们编写makefile的时候,应该依照以上原则编写。

target... : prerequisites...

recipe

...

...

每条规则一般都由一个或者多个target(目标)、prerequisites(依赖)以及recipe(处方)组成。当Make通过比较target和prerequisites的新旧来决定是否执行本条规则内的recipe,如果prerequisites比target的修改日期更新,则recipe被执行,否则不执行规则内的recipe。有一条值得注意:每一个recipe前面一定要先加一个tab制表符.

1、在目标为edit的规则中,使用了''将一个长行分隔为两行以方便阅读。

2、默认情况下,Make默认从Makefile的第一条规则开始执行,也就是说,当我们在shell中只敲下"make"并回车,make将会自动寻址当前目录下的Makefile并从其中的第一条规则开始执行。当然,我们也可以指定开始执行的规则

Example: make clean //从目标为clean的规则开始执行

3、在默认开始执行第一条规则edit时,由于目标依赖一些.o文件,而这些.o文件又有自己的更新规则,于是会先触发执行.o文件自己的更新规则,最后再回过头来执行edit。你可以将它理解为一个递归的过程。

4、很明显,由于clean这个目标并不是任何其他目标的依赖同时也不是第一条规则的目标,那么除非指定从这个规则开始执行,否则这个规则永远不会被执行;同样的,由于clean的规则没有任何依赖,这个规则执行时永远不会触发其他规则的执行。

规则是Makefile的重要组成部分,Make通过读取Makefile中的规则来决定如何更新工程文件。一般来说,一条规则分为三个部分:target、prerequisites和recipe.

如果没有特别指定从哪条规则开始执行,Make总是执行文件中的第一条规则,除此之外,其他规则的书写顺序对执行的先后没有影响(Make只在需要的时候执行需要的规则,而不是按书写顺序的先后执行).

虽然Makefile中的第一条规则是最先执行的,却往往是最后执行完的,因为第一条规则中的依赖部分经常有自己的更新规则,而那更新规则里的依赖又有对应的更新规则,这样层层递归,第一条规则触发了其他规则的执行,其他规则执行完后,再转回第一条规则继续执行。我们编译一份程序的时候也是这样,总是先编译每个子文件,再回过头将它们连接起来组成程序,因此,Makefile中的第一条规则一般是用于触发整个程序的编译(并且第一条规则的目标一般起名为:all,意指更新整个工程)

toolchain=gcc

OBJS=main.o modbus_cmd_generation.o software_crc.o

all:$(OBJS)

gcc modbus_cmd_generation.o main.o software_crc.o -o app

modbus_cmd_generation.o:modbus_cmd_generation.c modbus_cmd_generation.h software_crc.o

gcc modbus_cmd_generation.c -c

software_crc.o:software_crc.c software_crc.h

gcc software_crc.c -c

main.o:main.c

@echo

@echo compile the toolchain: $(toolchain)

@echo

gcc main.c -c

clean:

rm $(OBJS) app

在规则中,可以通过'$'来调用定义好的变量(如果希望真的打一个'$'而不是做变量引用,需要打"$$".

每条规则都有自己的recipes,其由一条或者多条shell指令组成,按照书写顺序执行。通常执行的结果是使得target被更新,默认调用/bin/sh来执行shell指令,可以手动更改.

也就是说,在Makefile中既有shell的指令,又有makefile自己的语句,所以说makefile遵循两种语法:在recipes中使用shell的语法,在其他部分遵循makefile自己的语法。make对于makefile中的recipes只进行有限的处理,然后就会丢给shell执行。

每个recipe一般用[TAB]字符开头,当然还有其他写法,不过我觉得目前知道这个就够用了

以[TAB]开头的空行同样算一条recipe,称为 empty recipe

在recipe中‘#'后的内容不会被作为注释,而是会原封不动的传递给shell

以[TAB]开头,在recipe中定义的变量同样会被当作shell变量原封不动传递给shell,而不是作为makefile的变量

今天的分享就到这里啦,EBYTE人每一天都致力于更好的助力物联化、智能化、自动化的发展,提升资源利用率,更多产品更多资料,感兴趣的小伙伴可以登录我们的亿佰特官网进行了解,还有客服小姐姐在线答疑哦!

7 X 24 销售服务热线

4000-330-990©© 成都亿佰特电子科技有限公司【版权所有】 蜀ICP备13019384号