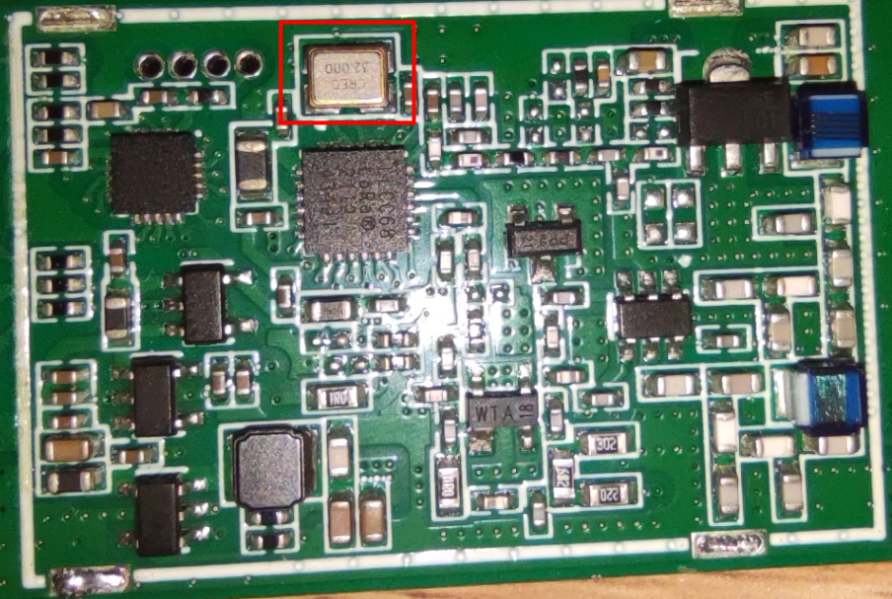

晶振是数字电路设计中关键先生,通常在电路设计当中,晶振都当作数字电路中的心脏部分,数字电路的所有工作都离不开时钟信号,而恰好晶振便是直接控制整个系统正常启动的那个关键按钮,可以说要是有数字电路设计的地方就可以看到晶振。

晶振一般是指石英晶体振荡器和石英晶体谐振器两种,也可以直接叫晶体振荡器。都是利用石英晶体的压电效应制作而成。

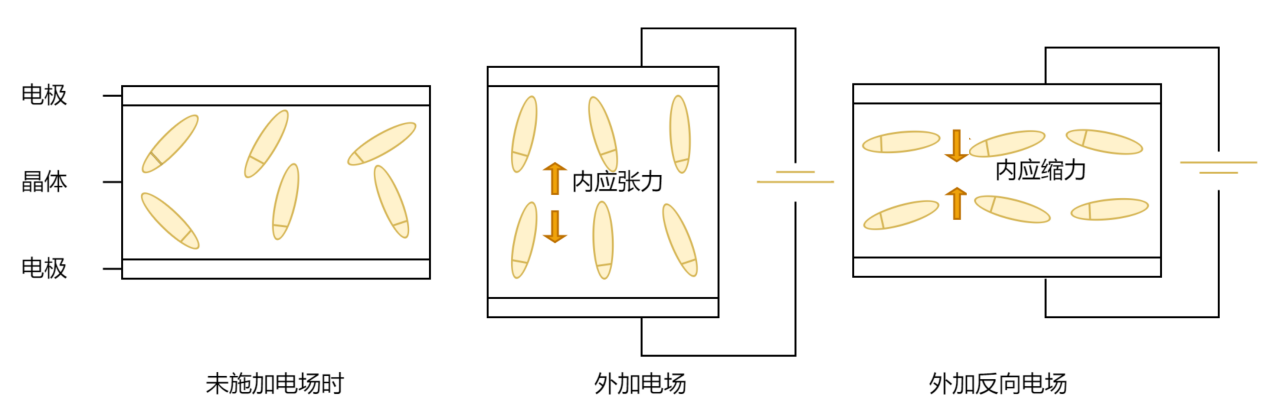

晶振的工作原理是这样的:在晶体两个电极上加上电场后,晶体会发生机械变形,相反的,若是在晶体的两端加上机械压力后,晶体又会产生电场。这种现象是可逆的,所以利用晶体的这种特性,在晶体两端加上交变电压,晶片就会产生机械振动,同时又会产生交变电场。但是晶体产生的这种振动和电场一般都会很小,但只要在某个特定频率下,振幅就会明显增大,就类似我们电路设计者常能见到的LC回路谐振同理。

无源晶振为晶体,一般是2引脚的无极性器件(部分无源晶振有无极性的固定引脚)。

无源晶振一般需借助于负载电容形成的时钟电路才能产生振荡信号(正弦波信号)。

有源晶振为振荡器,通常是4个引脚。有源晶振不需要CPU的内部振荡器,产生方波信号。有源晶振供电便能产生一个时钟信号。

有源晶振信号稳定,质量较好,而且连接方式比较简单,精度误差比无源晶振更小,价格比无源晶振更贵。

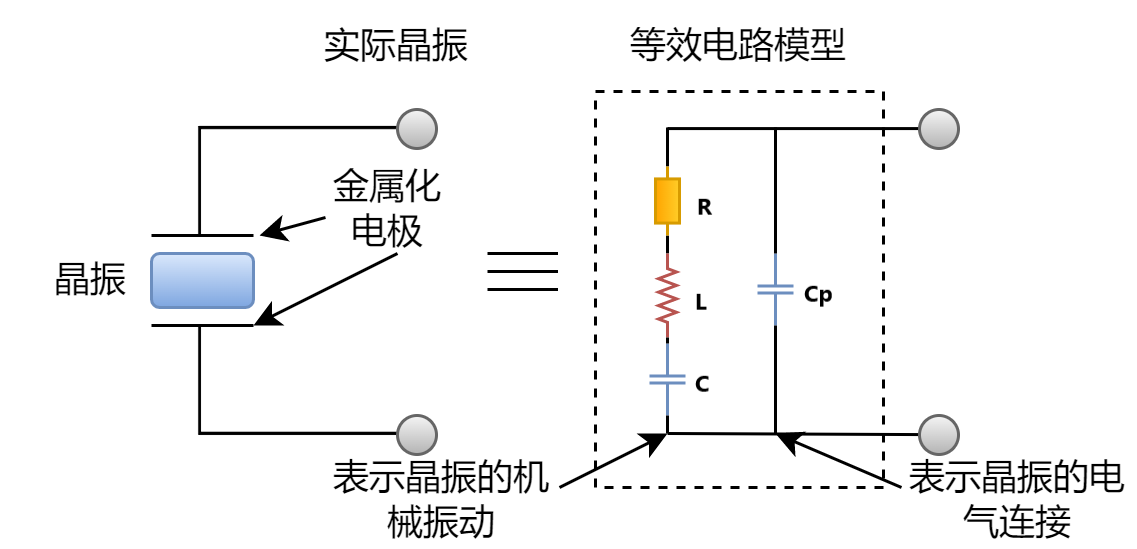

事实上,晶振的作用就像一个串联的RLC电路。

晶振的等效电路显示了一个串联的RLC电路,表示晶振的机械振动,与一个电容并联表示与晶振的电气连接,而晶振振荡器便朝着串联谐振运行工作。

其中,R是ESR等效串联电阻,L和C分别是等效电感和电容,Cp为寄生电容。

一般晶振的基本参数有:工作温度、精度值、匹配电容、封装形式、核心频率等。

晶振的核心频率:一般晶振频率的选择取决于频率元器件的要求规定,像MCU一般是一个范围,大部分都是从4M到几十M不等。

晶振的精度:晶振的精度普遍在±5PPM、±10PPM、±20PPM、±50PPM等,高精度的时钟芯片一般在±5PPM之内,一般运用都会选择在±20PPM左右。

晶振的匹配电容:通常通过调整匹配电容的值,可以更改晶振的核心频率,目前在做高精度晶振时,都是用该方法来进行调整。

作为数字电路中的心脏,晶振影响着整个系统的稳定性,系统晶振的选择,决定了数字电路的成败。

由于晶振内部存在石英晶体,受到外部撞击等情况造成晶体断裂,很容易造成晶振不启振,所以通常在电路设计时,要考虑晶振的可靠安装,其位置尽量不要靠近板边、设备外壳等地方。PCB对晶振布局时通常注意以下几点:

①晶振不能距离板边太近、晶振的外壳必须接地,否则易导致晶振辐射杂讯。

在板卡设计时尤其需要注意这点。外壳接地可以避免晶振向外辐射,同时可以屏蔽外来信号对晶振的干扰。如果一定要布置在PCB边缘,可以在晶振印制线边上再布一根GND线,同时在包地线上间隔一段距离就打过孔,将晶振包围起来。

②晶振下方不能布信号线,否则易导致信号线耦合晶振谐波杂讯。

保证完全铺地,同时在晶振的300mil范围内不要布线,这样可以防止晶振干扰其他布线、元器件和层的性能。

③若滤波器件放在晶振下方,且滤波电容与匹配电阻未按照信号流向排布,会使滤波器的滤波效果变差。

耦合电容应尽量靠近晶振的电源引脚,按电源流入方向,依容值从大到小顺序摆放。

④时钟信号的走线应尽量简短,线宽大一些,在布线长度和远离发热源上寻找平衡。

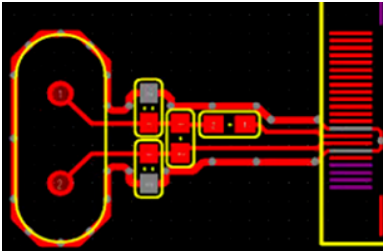

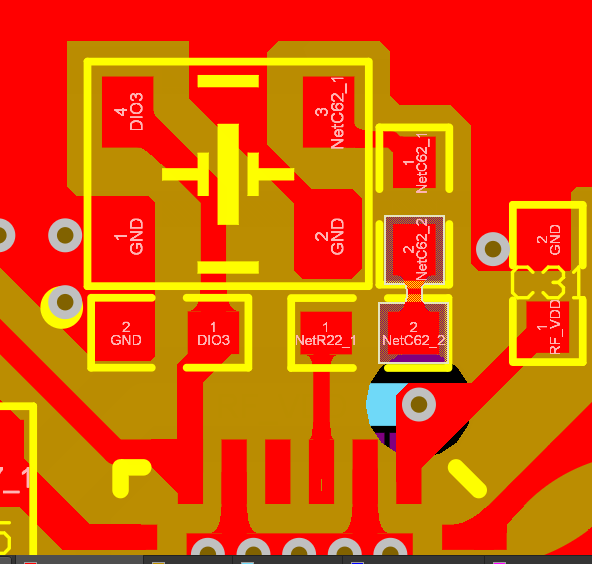

以下图布局为例,晶振的布局方式会相对更优:

①晶振的滤波电容与匹配电路靠近MCU芯片位置,远离板边。

②晶振的滤波电容与匹配电阻按照信号流向排布,靠近晶振摆放整齐紧凑。

③晶振靠近芯片处摆放,到芯片的走线尽量短而直。

在电路系统中,高速时钟信号线优先级最高。时钟线是一个敏感信号,频率越高,要求走线尽量简短,以保证信号的失真度达到最小。

因为现在很多电路中,系统晶振时钟频率很高,所以干扰谐波出来的能量也强,谐波除了会从输入与输出两条线导出来外,也会从空间辐射出来,这也导致若PCB中对晶振的布局不够合理,会很容易造成很强的杂散辐射问题,并且一旦产生,很难再通过其他方法来解决,所以在PCB板布局时对晶振和CLK信号线布局非常重要。

今天的分享就到这里啦,亿佰特人每一天都致力于更好的助力物联化、智能化、自动化的物联网应用发展,提升资源利用率,更多产品更多资料,感兴趣的小伙伴可以登录我们的官网进行了解,还有客服在线答疑哦!

7 X 24 销售服务热线

4000-330-990©© 成都亿佰特电子科技有限公司【版权所有】 蜀ICP备13019384号