差分电路是一种电子电路,其特征在于对共模信号的抑制和对差模信号的放大。共模信号和差模信号是信号传输中的两种重要形式。共模信号指的是两个信号在任意瞬时同时达到最大值或最小值,而差模信号则是两个信号在任意瞬时极性相反,大小相等。差分电路的分析也需要了解信号的共模和差模特性,以及电路的基本原理和电路分析方法。

共模干扰是在一般共同模式噪声的作用下与两个或多个信号输出发生的电压或电流干扰。它通常由接地干扰、电源干扰等因素引起,这些因素可能导致系统运行不稳定、数据错误等问题。

1、通过差模信号增加接地绝缘:在设计中使用绝缘放大器或绝缘变压器等元件,将信号的差模分离,避免差模信号对接地的影响。

2、降低共模噪声:通过设计合适的滤波器、使用低噪声电源等方法来降低共模噪声的水平,减少差模干扰。

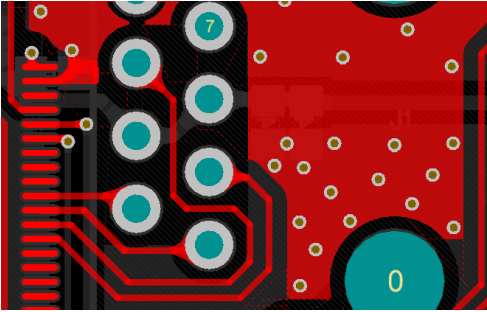

3、优化接地电路:在PCB设计中,合理规划接地布局,减少接地路径,降低接地电阻,避免形成环路等不良影响。

4、增加防护措施:采取屏蔽、屏蔽线等措施,保护外部电磁场,减少差动模块的干扰。

5、提高信号弹簧性能:通过使用适当的信号控制技术,如差分驱动和差分接收,可以提高信号弹簧的性能和抗干扰性能。

总之,消除差分模块的干扰需要综合考虑信号源、接收器、传输介质和接地等因素。以及相应的优化和改进措施。在高速PCB设计中越来越多地使用差分信号,并且电路中最重要的信号通常具有差分结构。

为什么这样呢?和普通的单端信号走线相比,差分信号有抗干扰能力强、能有效抑制EMI、时序定位精确的优势。

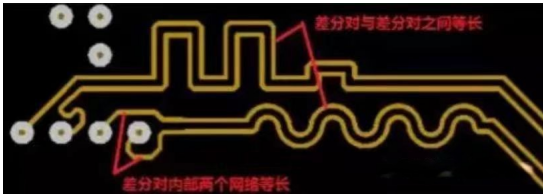

在电路板上,差分走线必须是等长、等宽、紧密靠近、且在同一层面的两根线。

▶ 等长:

等长是指两条线的长度要尽量一样长,是为了保证两个差分信号时刻保持相反极性。减少共模分量。

▶ 等宽、等距:

等宽是指两条信号的走线宽度需要保持一致,等距是指两条线之间的间距要保持不变,保持平行。

▶ 阻抗最小变化:

当设计具有差分信号的PCB时,最重要的事情之一是确定应用的目标阻抗并相应地规划差分对。此外,阻抗变化保持尽可能低。差分线路阻抗取决于线路宽度、线路耦合、铜厚度、PCB材料和堆叠等因素。当你试图避免任何改变差分阻抗的事情时,可考虑以上情况。

这种误解的原因是对表面现象的混淆或对高速信号传输机制的理解不足。差分电路对电源和地面上可能存在的类似和其他噪声信号是不敏感的。

在PCB电路设计中,差分线之间的耦合通常较低,通常为耦合度的10%至20%,更多的是对地耦合,因此差分走线的主要回流路径始终存在于地平面上。

当局部平面在没有参考平面的情况下断裂时,差分走线之间的耦合将提供主回路,虽然参考平面断裂对差分走线的影响对单端走线来说并不严重,但它降低了差分信号的质量,并可能地增加了EMI,所以要尽量避免。

在实际PCB布线中,差分设计的要求往往不能同时满足,由于脚管分布、过孔和步线空间等因素,必须通过适当的绕线来实现线路长度匹配的目标,但结果是:差分线的一部分不能平行。

PCB差分走线的设计中最重要的规则就是匹配线长,其它的规则都可以根据设计要求和实际应用进行灵活处理。

差分信号实际应用电路图

差分线的靠近只不过是加强它们的耦合,提高对噪声的免疫力,并充分利用磁场的相反极性来抵消外界的电磁场干扰。

虽然这种方法在大多数情况下非常有用的,但它不是绝对的,如果我们确保它们完全免受外部干扰,我们将不再需要允许彼此之间的强大通信来实现防止干扰和抑制EMI的目标。

增加与其他信号线的距离是最基本的方法之一,电磁场能量根据距离的平方关系减小,当线路之间的总距离是线路宽度的4倍时,它们之间的干扰非常微弱,基本上被忽略。。

此外,通过地平面的隔离也可以起到很好的屏蔽作用,这种结构在高频的(10G以上)IC封装PCB设计中经常会用采用,被称为CPW结构,可以保证严格的差分阻抗控制。

另外,通过地平面绝缘也可以起到很好的屏蔽作用,这种结构常用于高频(10g以上)IC外壳PCB结构,称为CPW结构,可实现严格的差分阻抗控制。

今天的分享就到这里啦,EBYTE每一天都致力于更好的助力物联化、智能化、自动化的发展,提升资源利用率,更多产品更多资料,感兴趣的小伙伴可以登录我们的亿佰特官网和企业公众号(微信号:cdebyte)进行了解,也可以直接拨打400电话咨询技术专员!

7 X 24 销售服务热线

4000-330-990深圳办事处柯经理:18218726658 北京办事处许经理:17692537861

常州办事处崔经理:15906110783 上海办事处周经理:17685308150

南京办事处葛经理:17626012283 杭州办事处戴经理:17512568697

武汉办事处石经理:18571355057 全国销售投诉电话:19934352316

业务邮箱:support@cdebyte.com

地址:四川省成都市高新西区西区大道199号B2、B5栋(前台座机:028-61543675)

©© 成都亿佰特电子科技有限公司【版权所有】 蜀ICP备13019384号-3