前文介绍了PCB设计指南、高效PCB走线布局设计、PCB电路板布局规则等等相关技术,本文会讲解在高速PCB电路板设计中为什么需要控制阻抗匹配,阻抗匹配是什么?阻抗有什么类型?影响PCB设计阻抗有哪些因素?

正确调整信号源的输出阻抗和负载阻抗,调整负载功率,抑制信号反射。其目的是确保信号或能量能够有效地从信号源传输到负载。

在低速PCB中可不使用电阻匹配,但在设计高速PCB时必须提供完整、可靠、准确、无干扰、无噪声的传输信号。因此,有必要确保PCB电路的特性反映在传输过程中,信号完整,传输损耗低,起到匹配阻抗的作用。如果关键信号与电阻不匹配,则可能导致信号反射、反弹、丢失等。

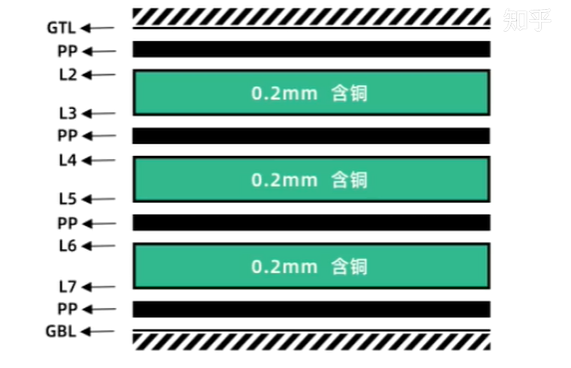

1、通过改变介质的厚度,阻抗的大小也会改变,介质的厚度是与阻抗成正比的;不同的半固化板具有不同的胶含量和厚度。压缩厚度取决于压力机布局和压板程序;对于所用的任何材料,都需要获得能产生的绝缘层厚度,以便于计算,而工程设计、压板控制、材料公差是调节介质厚度的关键。

图一介质厚度

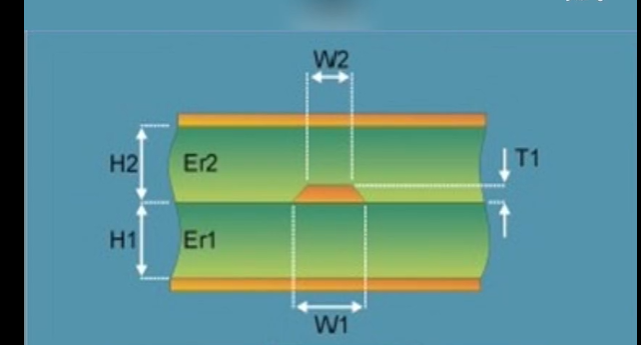

2、T-线宽,增加线宽可减小阻抗,减小线宽可增大阻抗。为了更好地满足阻抗测试线的要求,需要±10%的公差来控制线宽。阻抗测试线的击穿影响整个测试波形,其单点电阻高,导致整个波形不对齐,不允许有阻抗线,击穿不超过10%。线宽主要受刻蚀控制。为保证线宽,应根据刻蚀、光刻误差、图形剪切误差和技术底片补偿技术,满足线宽要求。

图二线宽

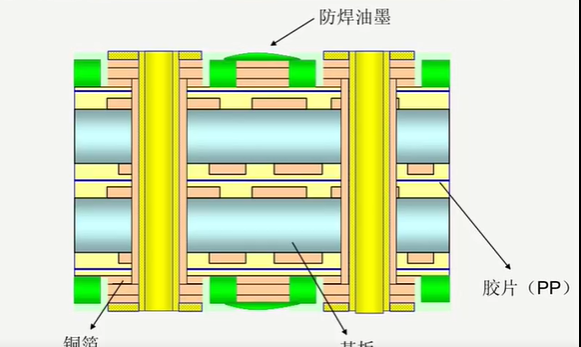

3、铜越厚、导线越细,阻抗越大;导线越粗,阻抗越小。导线的厚度可以通过样品电镀或选择具有适当厚度的基板来控制。铜厚度应控制均匀。在细线和绝缘线板上添加旁路块,以平衡电流,避免线路上的铜厚度不均匀,影响阻抗,并使CS和SS表面上的铜分布不均匀。为了在两侧实现均匀的铜厚度,必须将板拉过。

图三铜厚

4、Er-介电常数,不同的板子材料介电常数是有区别的,常见的板子材料有纸基板、环氧玻纤布基板(FR4比较常用)、复合基板,常用的就是FR4,这种材料的Er特性是随着加载频率的不同变化而变化,在使用频率为1GHZ以下认为4.2左右,1.5-2.0GHZ的使用频率下会有所下降,故在实际应用时需要注意产品的使用频率。

图四介电常数示意图

5、电阻焊厚度、压力电阻焊降低了外层阻抗。在正常情况下,电阻焊打印一次可以使单端减少2欧姆,差分减少8欧姆。打印两次的减少值是打印一次的两倍。如果打印三次以上,阻抗值不会改变。

图五阻焊厚度示意图

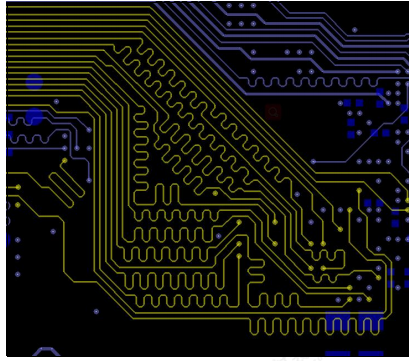

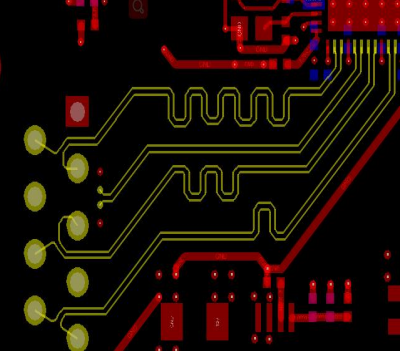

第一个是一个单线的微带线,第二个是差分的带状线,当然微带线也可以有差分,带状线也可以有单端。

在多层板中,单向和微分导线是指相邻的层。需要注意的是,RF线处理被称为中间层,提供最佳RF天线宽度以实现最佳性能。所谓并联电阻是指需要电阻匹配的单向或多方向线路,通常在信号线两侧包含铜板,以实现电阻匹配的目标。如图:

图六多层板单端阻抗

图七多层板差分阻抗

图八射频单端阻抗的隔层参考处理

不同信号的阻抗值不同,例如90Ω、100Ω、120Ω等。不是所有的线都有阻抗匹配的要求。通用USB2.0需要90Ω阻抗、HDMI、USB3.0、MIPI、100兆端口、千兆端口和其他控制,通常为100Ω阻抗、RS422为120Ω。单极线通常是50Ω的反电阻,理想模型下是50Ω。然而,事实上全源极电阻不是50Ω,负载连接电阻也不是50Ω。此时,需要几个电阻触点,适当的电路由电感和电容组成。同时,我们需要使用电容器和电感器来调试电阻调谐电路,以实现最佳的RF特性。

今天的分享就到这里啦,亿佰特人每一天都致力于更好的助力物联化、智能化、自动化的发展,提升资源利用率,更多产品更多资料,感兴趣的小伙伴可以登录我们的官网进行了解,还有客服小姐姐在线答疑哦!

7 X 24 销售服务热线

4000-330-990深圳办事处柯经理:18218726658 北京办事处许经理:17692537861

常州办事处崔经理:15906110783 上海办事处周经理:17685308150

南京办事处葛经理:17626012283 杭州办事处戴经理:17512568697

全国销售投诉电话:19934352316 业务邮箱:support@cdebyte.com

地址:四川省成都市高新西区西区大道199号B5栋(前台座机:028-61543675)

©© 成都亿佰特电子科技有限公司【版权所有】 蜀ICP备13019384号-3